I recently purchased a ROM 01 Apple IIgs with the intention of using it to further my disk image explorations. While it came with an Apple 1MB expansion card, I quickly realized that it would be useful to have more memory installed.

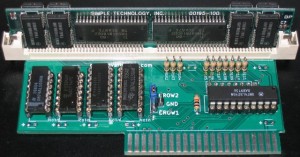

In searching for information regarding the memory expansion capabilities, I came across the postings outlining the RAMGS expansion boards from http://gglabs.us/ In it, the developer notes how it is possible to use FPM DRAM in place of the standard DRAM chips. I realized that these same chips are those used on standard PC SIMMs.

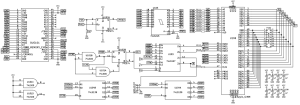

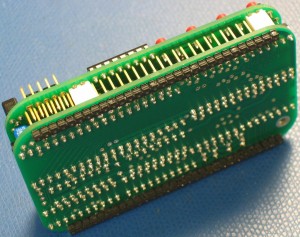

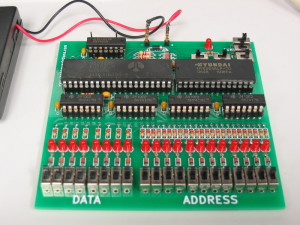

Analyzing the circuits used by GGlabs, and comparing the memory portion to that of a standard SIMM, I realized that some simplifications can be made. In particular, the SIMM multiplexes four CAS and four RAS signals to select the byte being read, this means that one of the dual 2:4 decoders can be eliminated by feeding the correct inputs into a single 2:4 decoder.

Due to the way that the IIgs performs memory refresh, it is important to ensure that both 4MB banks be refreshed together. This is done by using a quad 2:1 mux. The mux applies the correct input to the 2:4 decoder to ensure that CAS0 and CAS2 (for the first 4MB bank) are selected and that they are routed also to CAS1 and CAS3 (for the second 4MB bank.) The final 2:1 multiplexer is used to ensure that the write line is high during a refresh, as outlined in the GGlabs reference.

While testing a random assortment of 4MB and 8MB SIMMs that I have collected over the years, I found that this circuit works with EDO SIMMs as well as FPM SIMMs.