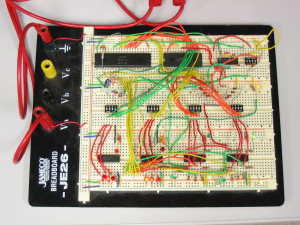

While working on my mini OSI-300 Trainer, I encountered issues with the switches that I had purchased. The seller advertised them as SS12D07 switches, which according to the data sheets that I had found, were non-shorting, single pole, double throw switches.

They were single throw, double pole, and fit the size and shape specifications. Unfortunately, the ones I received were definitely not non-shorting, otherwise known as break before make, switches. I found a single SS12D02 from Jameco in among my assortment of switches. It appears to be non-shorting, and taking it apart I found that it uses a slightly different mechanism than the SS12D07 I had purchased.

I placed an order for C&K OS102011MS2QN1 switches, which are designed to be non-shorting (there is a specific shorting version.) The C&K parts arrived and I have tested and confirmed that they are definitely non-shorting as expected.

In the images above, I show the parts from left to right:

- Jameco SS12D02

- C&K OS102011MS2QN1

- T.O.Y SS12D07 (shorting)

Both the Jameco and C&K parts have two small vertical slots on the side. The T.O.Y part has an indentation on the opposite side, which can be seen in the second image.

For my mini OSI-300, the T.O.Y parts are usable for all but the Run and Reset switches. The Data and Address switches are configured as single pole, single throw. The NMI switch has a resistor to prevent a direct short to ground, and the ROM switch does not switch between power and ground directly. The Load switch is configured as a double pole, single throw switch as well.

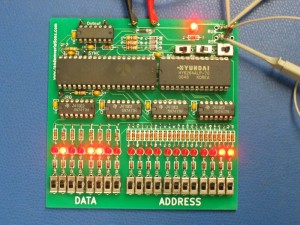

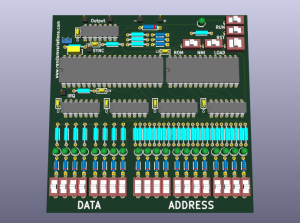

In general, I have had the expected results when purchasing parts from places other than the big parts houses such as Mouser, Digi-key, Jameco, etc. I find that looking closely at images and reviews improves the odds of receiving a working part. Out of the ten 6264 SRAM chips I received, although all were marked with the same markings on top, they all had different tool marks on the body, markings on the backside, and three were completely non-functional.